## DESIGN AND ANALYSIS OF UPDATE-BASED CACHE COHERENCE PROTOCOLS FOR SCALABLE SHARED-MEMORY MULTIPROCESSORS

David Brian Glasco

Technical Report No. CSL-TR-95-670

June 1995

This research was Supported by Digital Equipment Corporation and Sun Microsystems, Inc.

### DESIGN AND ANALYSIS OF UPDATE-BASED CACHE COHERENCE PROTOCOLS FOR SCALABLE SHARED-MEMORY MULTIPROCESSORS

by

David Brian Glasco

Technical Report No. CSL-TR-95-670 June 1995

Computer Systems Laboratory Department of Electrical Engineering and Computer Science Stanford University Stanford, California 94305

#### Abstract

This dissertation examines the performance difference between invalidate-based and update-based cache coherence protocols for scalable shared-memory multiprocessors. The first portion of the dissertation reviews cache coherence. First, chapter 1 describes the cache coherence problem and identifies the two classes of cache coherence protocols, invalidate-based and update-based. The chapter also reviews bus-based protocols and reviews the additional requirements placed on the protocols to extend them to scalable systems. Next, chapter 2 reviews two latency tolerating techniques, relaxed memory consistency models and software-controlled data prefetch, and examines their impact on the cache coherence protocols. Finally, chapter 3 reviews the details of three invalidate-based protocols defined in the literature and defines two new update-based protocols.

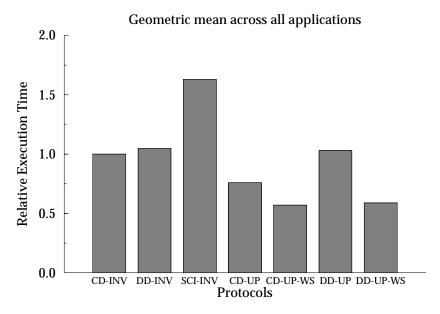

The second portion of this dissertation examines the performance differences between invalidate-based and update-based protocols. First, chapter 4 presents the methodology used to examine the performance of the protocols. This presentation includes a discussion of the simulation environment, the simulated architecture and the scientific applications. Next, chapter 5 describes and analyzes the performance of two enhancements to the update-based cache coherence protocols. The first enhancement, a fine-grain or word based synchronization scheme, combines data synchronization with the data. This allows the system to take advantage of the fine-grain data updates which result from the update-based protocols. The second enhancement, a write grouping scheme, is necessary to reduce the network traffic generated by the update-based protocols. Next, chapter 6 presents and discusses the simulated results that demonstrate that update-based protocols, with the two enhancements, can significantly improve the performance of the fine-grain scientific applications examined compared to invalidate-based protocols. Chapter 7 examines the sensitivity of the protocols to changes in the architectural parameters and to migratory data. Finally chapter 8 discusses how the choice of protocols affect the correctness, cost and efficiency of the cache coherence mechanism.

Overall, this work demonstrates that update-based protocols can be used not only as a coherence mechanism, but also as a latency reducing and tolerating technique to improve the performance of a set of fine-grain scientific applications. But as with other latency reducing techniques, such as data prefetch, the technique must be used with an understanding of its consequences.

© Copyright 1995 by David Brian Glasco All Rights Reserved

## Acknowledgements

First, I would like to thank my wife Reem for without her love and support, especially her hugs, none of this work would have been possible. I would also like to thank my parents who instilled in me the desire and ambition required to complete such an undertaking.

Next, I would like to thank my advisors, Bruce Delagi and Michael Flynn, who gave me excellent guidance throughout this endeavor. I especially would like to thank Bruce for seeing my potential and offering me support early in my academic career.

I would like to thank Manu Thapar for helping me understand the cache coherence problem and some of the possible solutions and Nakul Saraiya for answering my endless questions about the simulator and LISP.

Finally, I would like to thank Sun Microsystems for providing me with office space and more machines than I could ever use.

# Contents

## Acknowledgements

| 1        | Intr           | roduction                               | 1         |

|----------|----------------|-----------------------------------------|-----------|

|          | 1.1            | Parallel Processors                     | 1         |

|          | 1.2            | Shared-Memory Multiprocessors           | 1         |

|          | 1.3            | Cache Coherence                         | 3         |

|          |                | 1.3.1 Broadcast-Based Protocols         | 5         |

|          |                | 1.3.2 Directory-Based Protocols         | 8         |

|          | 1.4            | Organization of Dissertation            | 11        |

|          | 1.5            | Contributions of Dissertation           | 11        |

| <b>2</b> | Lat            | ency Reducing and Tolerating Techniques | 13        |

|          | 2.1            | Memory Consistency Models               | 13        |

|          |                | 2.1.1 Sequential Consistency Model      | 15        |

|          |                | 2.1.2 Processor Consistency Model       | 19        |

|          |                | 2.1.3 Weak Consistency Model            | 20        |

|          |                | 2.1.4 Release Consistency Model         | 21        |

|          |                | 2.1.5 Summary                           | 22        |

|          | 2.2            | Software-Controlled Data Prefetch       | 23        |

|          | 2.3            | Summary                                 | 25        |

| 3        | $\mathbf{Dir}$ | ectory-Based Protocols                  | <b>26</b> |

|          | 3.1            | Directory Structures                    | 26        |

|          |                | 3.1.1 Centralized Directory             | 27        |

iv

|          |     | 3.1.2   | Distributed Directory                        | 27 |

|----------|-----|---------|----------------------------------------------|----|

|          |     | 3.1.3   | Scalability of Directory Structures          | 29 |

|          | 3.2 | Protoc  | col Deadlock                                 | 30 |

|          | 3.3 | Invalie | date-Based Protocols (INV)                   | 33 |

|          |     | 3.3.1   | Centralized Directory (CD-INV)               | 33 |

|          |     | 3.3.2   | Distributed Directory                        | 39 |

|          |     | 3.3.3   | Singly-Linked Distributed Directory Protocol | 39 |

|          |     | 3.3.4   | Doubly-Linked Directory Directory Protocol   | 43 |

|          |     | 3.3.5   | Summary                                      | 45 |

|          | 3.4 | Updat   | e-Based Protocol (UP)                        | 46 |

|          |     | 3.4.1   | Centralized Directory (CD-UP)                | 46 |

|          |     | 3.4.2   | Distributed Directory (DD-UP)                | 60 |

|          | 3.5 | Protoc  | col Verification                             | 74 |

|          | 3.6 | Summ    | nary                                         | 76 |

| 4        | Sim | ulatio  | n Methodology                                | 77 |

|          | 4.1 | Syster  | n Architecture                               | 77 |

|          |     | 4.1.1   | Processor Model                              | 79 |

|          |     | 4.1.2   | Write Buffer                                 | 79 |

|          |     | 4.1.3   | Cache Model                                  | 79 |

|          |     | 4.1.4   | Directory/Memory Model                       | 79 |

|          |     | 4.1.5   | Bus Model                                    | 80 |

|          |     | 4.1.6   | Network Model                                | 80 |

|          | 4.2 | Simula  | ation Environment                            | 81 |

|          |     | 4.2.1   | Basic Objects                                | 81 |

|          |     | 4.2.2   | Node Object                                  | 83 |

|          | 4.3 | Scient  | ific Application Domain                      | 86 |

| <b>5</b> | Enh | ancer   | nents to Update-Based Protocols              | 88 |

|          | 5.1 |         | Synchronization                              | 88 |

|          |     | 5.1.1   | Block Synchronization                        | 89 |

|          |     | 5.1.2   | Word Synchronization                         | 90 |

|   |     | 5.1.3           | Performance of Block Synchronization                                                                                                                | 91  |

|---|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |     | 5.1.4           | Performance of Word Synchronization                                                                                                                 | 94  |

|   |     | 5.1.5           | Performance Impact of Data Prefetching                                                                                                              | 99  |

|   |     | 5.1.6           | Performance of Word Synchronization Compared to Block Syn-                                                                                          |     |

|   |     |                 | $chronization \ldots \ldots$ | 101 |

|   |     | 5.1.7           | Relative Performance of Word Synchronization Compared to a                                                                                          |     |

|   |     |                 | Common Base                                                                                                                                         | 105 |

|   |     | 5.1.8           | Summary                                                                                                                                             | 107 |

|   | 5.2 | Write           | Grouping                                                                                                                                            | 108 |

|   |     | 5.2.1           | Software-Based Write Grouping                                                                                                                       | 109 |

|   |     | 5.2.2           | Hardware-Based Write Grouping                                                                                                                       | 111 |

|   |     | 5.2.3           | Grouped Update Network Packet                                                                                                                       | 113 |

|   |     | 5.2.4           | Write Grouping Performance                                                                                                                          | 114 |

|   |     | 5.2.5           | Variations in Hardware-Based Grouping                                                                                                               | 116 |

|   |     | 5.2.6           | Summary                                                                                                                                             | 120 |

| 6 | Per | forma           | nce Results                                                                                                                                         | 122 |

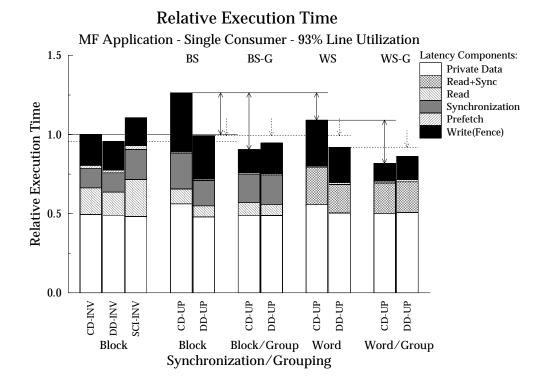

|   | 6.1 | MF A            | pplication                                                                                                                                          | 124 |

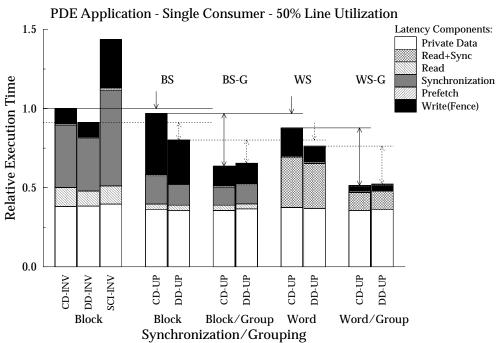

|   | 6.2 | PDE .           | Application                                                                                                                                         | 126 |

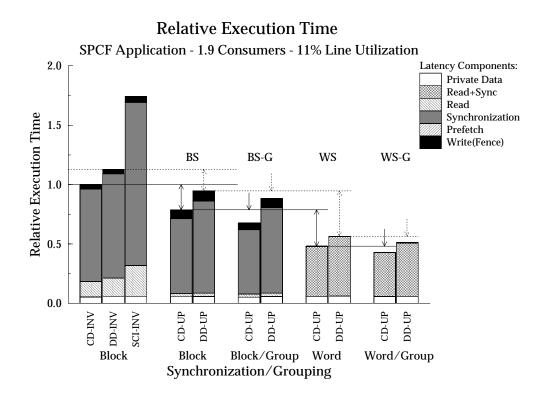

|   | 6.3 | SPCF            | Application                                                                                                                                         | 128 |

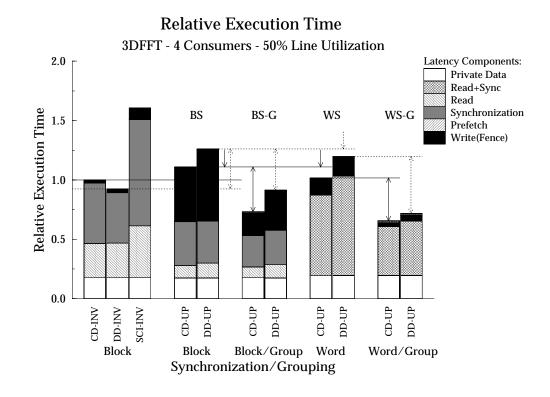

|   | 6.4 | $3\mathrm{DFF}$ | T Application $\ldots$                                             | 130 |

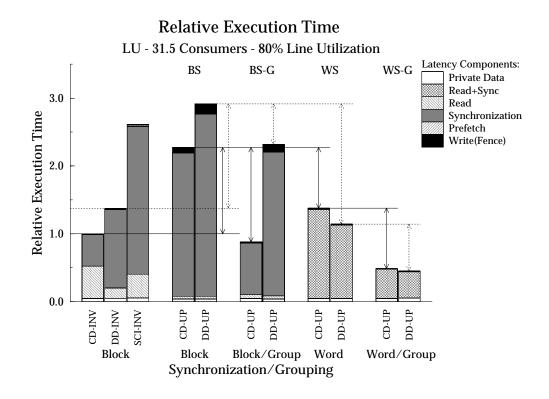

|   | 6.5 | LU A            | pplication                                                                                                                                          | 132 |

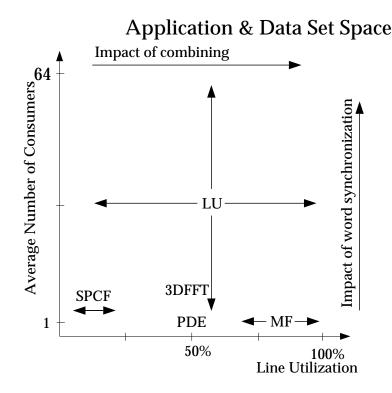

|   | 6.6 | Summ            | nary                                                                                                                                                | 133 |

| 7 | Sen | sitivit         | y of Protocols                                                                                                                                      | 138 |

|   | 7.1 | Archit          | tecture Parameter Sensitivity                                                                                                                       | 138 |

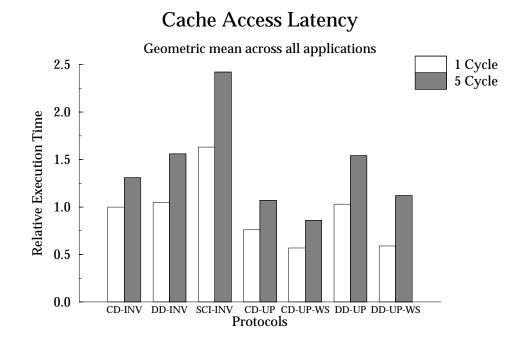

|   |     | 7.1.1           | Cache Access Time                                                                                                                                   | 139 |

|   |     | 7.1.2           | Directory Access Time                                                                                                                               | 141 |

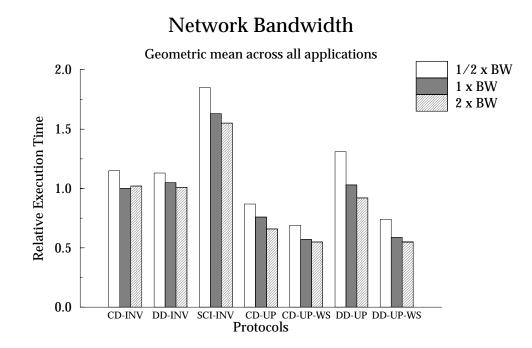

|   |     | 7.1.3           | Network Bandwidth                                                                                                                                   | 142 |

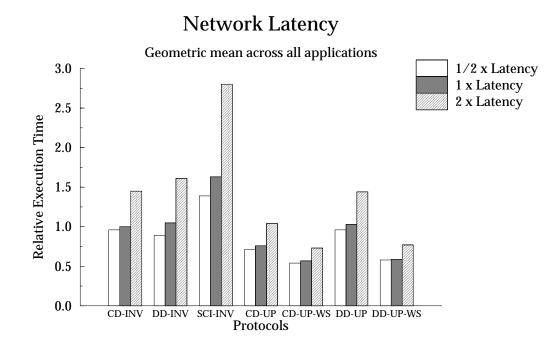

|   |     | 7.1.4           | Network Latency                                                                                                                                     | 144 |

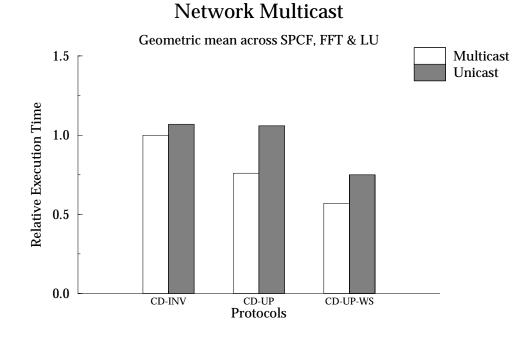

|   |     | 7.1.5           | Network Multicast                                                                                                                                   | 146 |

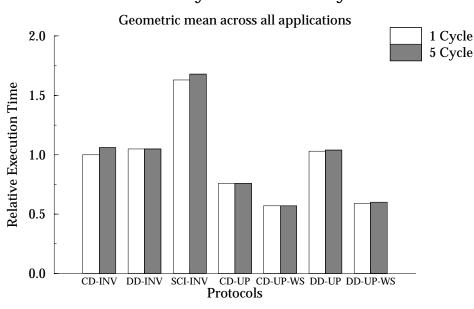

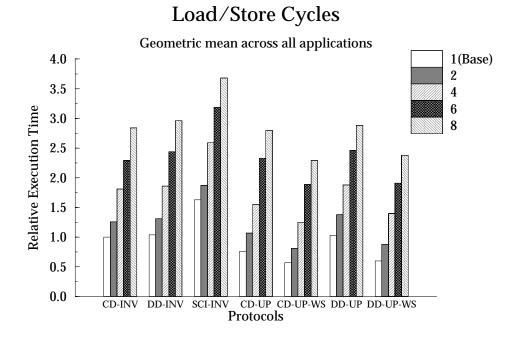

|   |     | 7.1.6           | Load/Store Cycles                                                                                                                                   | 147 |

|   |      | 7.1.7 Summary                        | 149 |

|---|------|--------------------------------------|-----|

|   | 7.2  | Migratory Data                       | 150 |

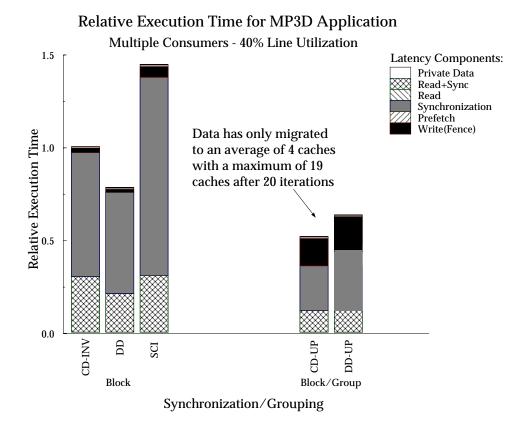

|   |      | 7.2.1 MP3D Application               | 151 |

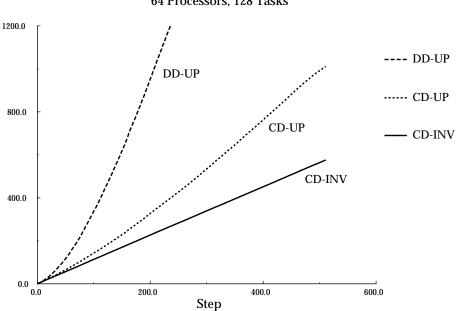

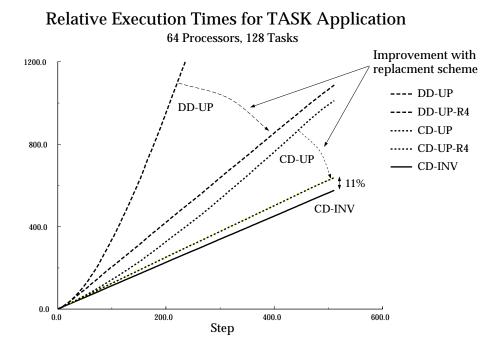

|   |      | 7.2.2 Synthetic Task Application     | 152 |

| 8 | Con  | clusions and Future Work             | 157 |

|   | 8.1  | Correctness                          | 157 |

|   | 8.2  | Cost of Protocol Implementation      | 158 |

|   | 8.3  | Efficiency of Protocols              | 159 |

|   | 8.4  | Summary                              | 161 |

|   | 8.5  | Future Work                          | 162 |

| A | Scie | entific Applications                 | 163 |

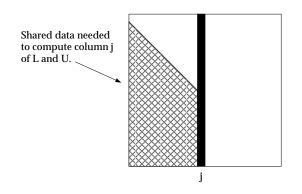

|   | A.1  | Multifrontal Solver (MF)             | 163 |

|   |      | A.1.1 Algorithm                      | 163 |

|   |      | A.1.2 Implementation                 | 164 |

|   | A.2  | Simple Iterative PDE Solver (PDE)    | 166 |

|   |      | A.2.1 Algorithm                      | 166 |

|   |      | A.2.2 Implementation                 | 167 |

|   | A.3  | Sparse Cholesky Decomposition (SPCF) | 168 |

|   |      | A.3.1 Algorithm                      | 168 |

|   |      | A.3.2 Implementation                 | 169 |

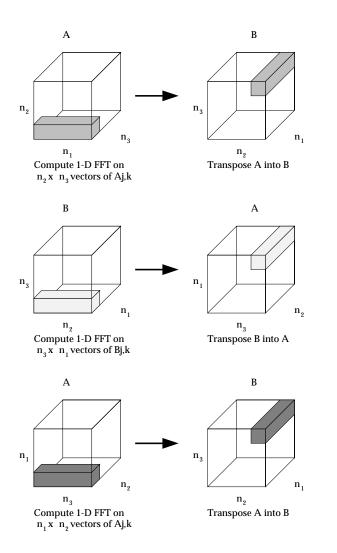

|   | A.4  | 3D PDE Solver using FFTs (3DFFT)     | 170 |

|   |      | A.4.1 Algorithm                      | 170 |

|   |      | A.4.2 Implementation                 | 171 |

|   | A.5  | LU Decomposition (LU)                | 173 |

|   |      | A.5.1 Algorithm                      | 173 |

|   |      | A.5.2 Implementation                 | 173 |

|   | A.6  | Summary of Scientific Applications   | 175 |

| в | Mig  | gratory Data Applications            | 176 |

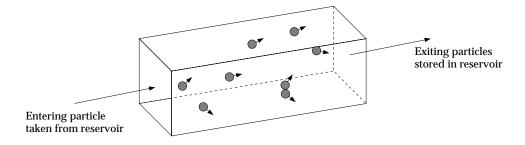

|   | B.1  | MP3D Particle Simulator              | 176 |

|              |       | B.1.1 Algorithm                 | 176 |

|--------------|-------|---------------------------------|-----|

|              |       | B.1.2 Implementation            | 177 |

|              | B.2   | Synthetic Task Application      | 177 |

| $\mathbf{C}$ | Tab   | les of Relative Execution Times | 179 |

|              | С.1   | Base Simulation Times           | 179 |

|              | C.2   | Sensitivity Simulation Times    | 179 |

| Bi           | bliog | raphy                           | 184 |

# List of Tables

| 3.1                                    | CD-UP: Description of Messages                                      | 48                                        |

|----------------------------------------|---------------------------------------------------------------------|-------------------------------------------|

| 3.2                                    | CD-UP: Messages That May Deadlock                                   | 58                                        |

| 3.3                                    | DD-UP: Description of Messages                                      | 62                                        |

| 3.4                                    | DD-UP: Messages That May Deadlock                                   | 72                                        |

| 3.5                                    | Protocol Summary                                                    | 76                                        |

| 5.1                                    | Ratio of Invalidation/Update Count for Word Compared to Block Syn-  |                                           |

|                                        | chronization                                                        | 103                                       |

| 5.2                                    | Ratio of Network Traffic for Word Compared to Block Synchronization | 103                                       |

| 5.3                                    | Grouping Efficiency - Words Per Update Packet                       | 115                                       |

| 5.4                                    | HW Grouping Delay (Cycle) - Words Per Write Group                   | 117                                       |

| 5.5                                    | Grouping Location - Words Per Write Group                           | 119                                       |

|                                        |                                                                     |                                           |

| A.1                                    | Characteristics of Multifrontal Solver Application                  | 166                                       |

| A.1<br>A.2                             | Characteristics of Multifrontal Solver Application                  | 166<br>168                                |

|                                        |                                                                     |                                           |

| A.2                                    | Characteristics of PDE Application                                  | 168                                       |

| A.2<br>A.3                             | Characteristics of PDE Application                                  | $\begin{array}{c} 168 \\ 170 \end{array}$ |

| A.2<br>A.3<br>A.4                      | Characteristics of PDE Application                                  | 168<br>170<br>171                         |

| A.2<br>A.3<br>A.4<br>A.5               | Characteristics of PDE Application                                  | 168<br>170<br>171<br>174                  |

| A.2<br>A.3<br>A.4<br>A.5<br>A.6        | Characteristics of PDE Application                                  | 168<br>170<br>171<br>174<br>175           |

| A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>B.1 | Characteristics of PDE Application                                  | 168<br>170<br>171<br>174<br>175<br>177    |

| C.3 | Directory Access (5 Cycle) Relative Execution Times | 180 |

|-----|-----------------------------------------------------|-----|

| C.4 | Network Bandwidth Relative Execution Times          | 181 |

| C.5 | Network Latency Relative Execution Times            | 181 |

| С.6 | Relative Execution Times Without Multicast          | 182 |

| C.7 | Processor Load/Store Cycle Count                    | 183 |

# List of Figures

| 1.1  | Uniform Memory Access (UMA) Model                            | 2  |

|------|--------------------------------------------------------------|----|

| 1.2  | Non-Uniform Memory Access (NUMA) Model                       | 3  |

| 1.3  | Cache Coherence Problem                                      | 4  |

| 1.4  | Protocol Classes                                             | 5  |

| 1.5  | Berkeley Invalidate-Based Cache Coherence Broadcast Protocol | 7  |

| 1.6  | Dragon Update-Based Cache Coherence Broadcast Protocol       | 9  |

| 1.7  | Directory-Based Cache Coherence Protocols                    | 10 |

| 2.1  | Sequential Consistency - Invalidate-Based Protocols          | 17 |

| 2.2  | Violating Sequential Consistency - Update-Based Protocols    | 18 |

| 2.3  | Block Synchronization with Prefetch                          | 24 |

| 3.1  | Centralized Directory Structure                              | 27 |

| 3.2  | Singly-Linked Distributed Directory Structure                | 28 |

| 3.3  | Doubly-Linked Distributed Directory Structure                | 29 |

| 3.4  | Protocol Level Deadlock                                      | 31 |

| 3.5  | CD-INV: Read Miss to Absent or Shared Memory Line            | 34 |

| 3.6  | CD-INV: Read Miss to <i>Exclusive</i> Memory Line            | 35 |

| 3.7  | CD-INV: Write Miss to <i>Shared</i> Memory Line              | 36 |

| 3.8  | CD-INV: Write Miss to <i>Exclusive</i> Memory Line           | 37 |

| 3.9  | CD-INV: Write Request                                        | 38 |

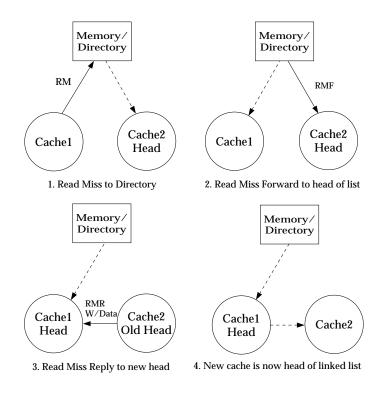

| 3.10 | DD-INV: Read Miss                                            | 40 |

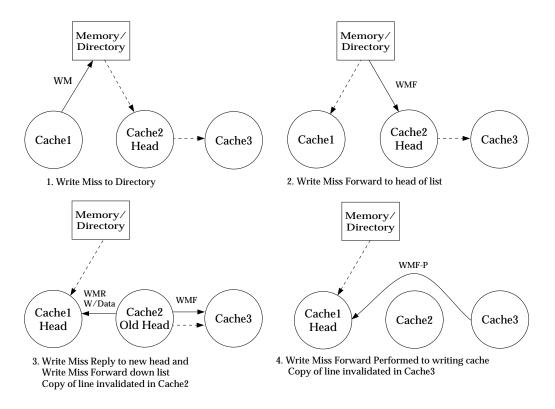

| 3.11 | DD-INV: Write Miss                                           | 41 |

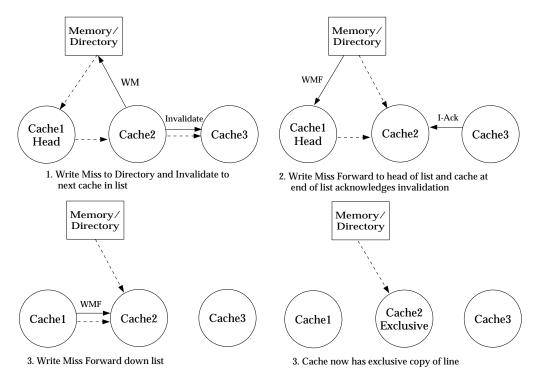

| 3.12 | DD-INV: Write Request                                        | 42 |

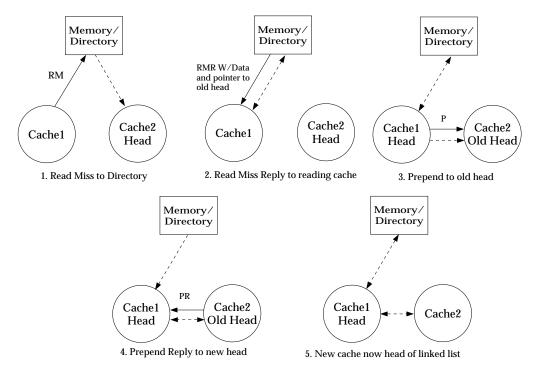

| 3.13 | SCI-INV: Read Miss to Valid Memory Line                  | 44 |

|------|----------------------------------------------------------|----|

| 3.14 | SCI-INV: Write Miss to Clean Line                        | 45 |

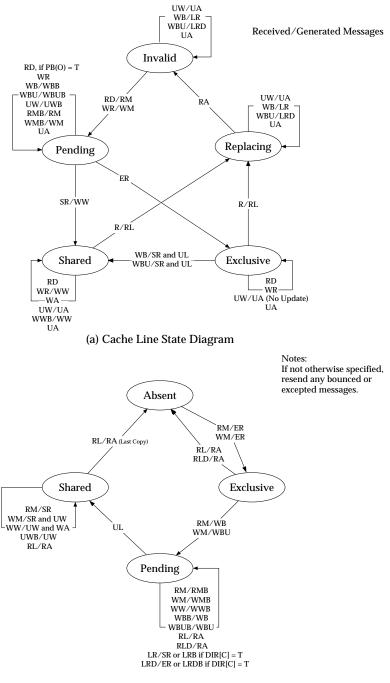

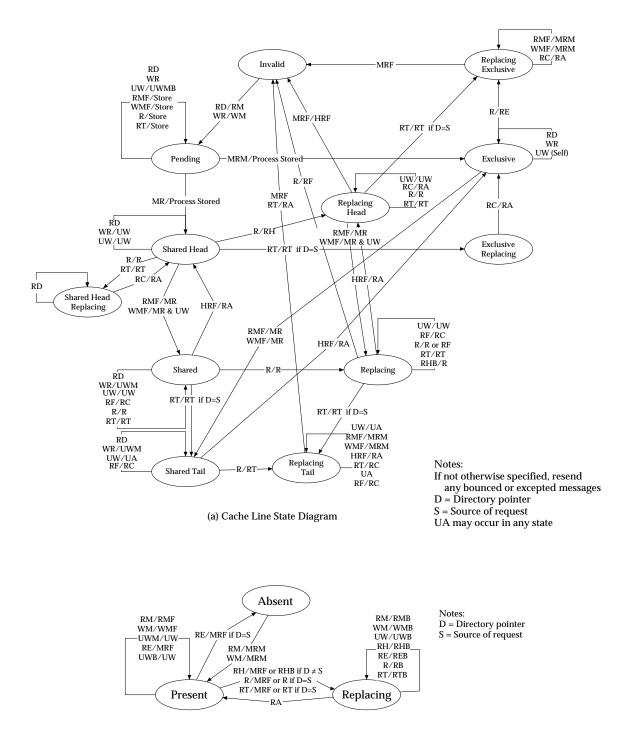

| 3.15 | CD-UP: Cache and Memory Line State Diagrams              | 49 |

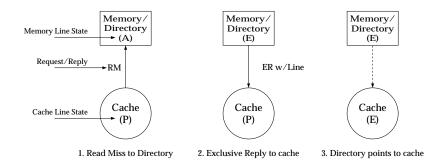

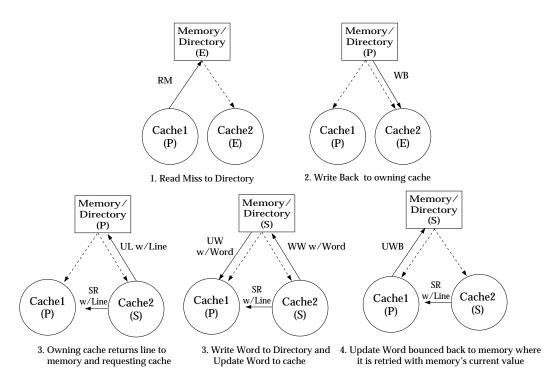

| 3.16 | CD-UP: Read Miss to Absent Memory Line                   | 51 |

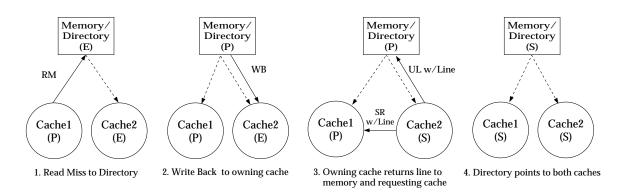

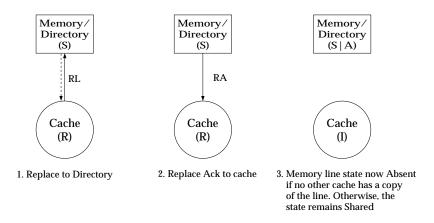

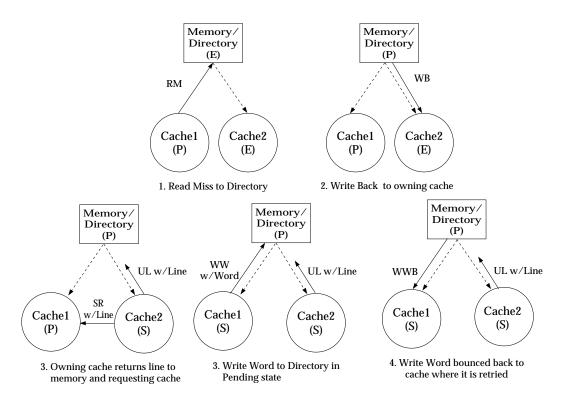

| 3.17 | CD-UP: Read Miss to <i>Exclusive</i> Memory Line         | 51 |

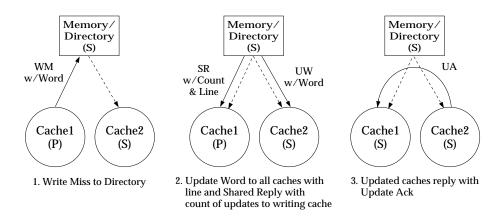

| 3.18 | CD-UP: Write Miss to <i>Shared</i> Memory Line           | 52 |

| 3.19 | CD-UP: Write Hit to <i>Shared</i> Memory Line            | 53 |

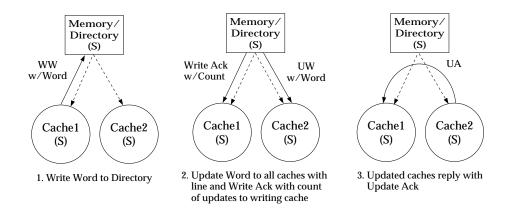

| 3.20 | CD-UP: Replacing Cache Line in the <i>Shared</i> State   | 54 |

| 3.21 | CD-UP: Race: Write Word to <i>Pending</i> Memory Line    | 55 |

| 3.22 | CD-UP: Race: Update Word to <i>Pending</i> Cache Line    | 56 |

| 3.23 | CD-UP: Race: Write Back to <i>Pending</i> Cache Line     | 57 |

| 3.24 | CD-UP: Race: Line Replaced to <i>Pending</i> Memory Line | 59 |

| 3.25 | DD-UP: Cache and Memory Line State Diagrams              | 63 |

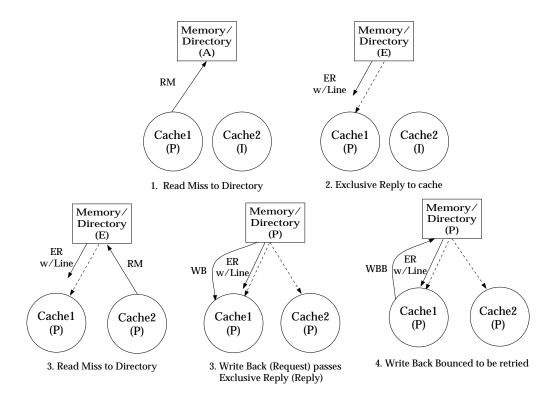

| 3.26 | DD-UP: Read Miss to Absent Memory Line                   | 64 |

| 3.27 | DD-UP: Read Miss to Present Memory Line                  | 64 |

| 3.28 | DD-UP: Write Miss to <i>Present</i> Memory Line          | 65 |

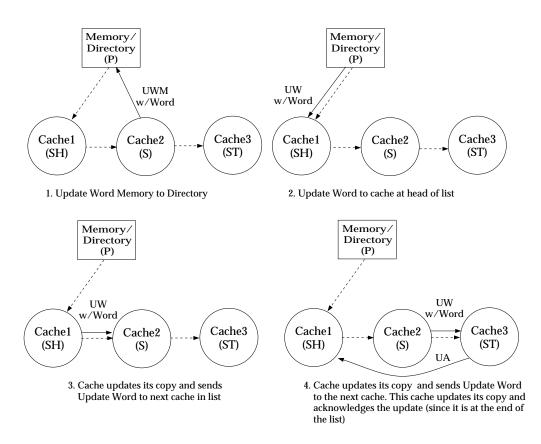

| 3.29 | DD-UP: Write Hit to Cache Line in Shared Head State      | 66 |

| 3.30 | DD-UP: Write Hit from Cache Line in <i>Shared</i> State  | 67 |

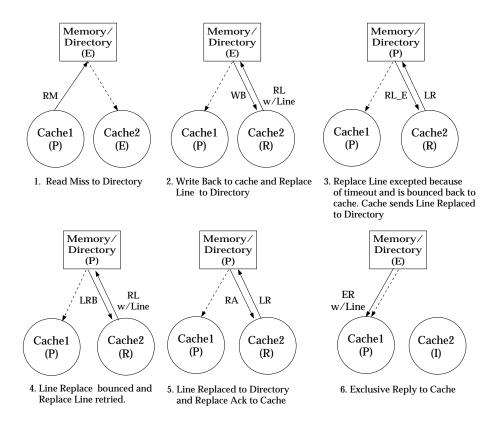

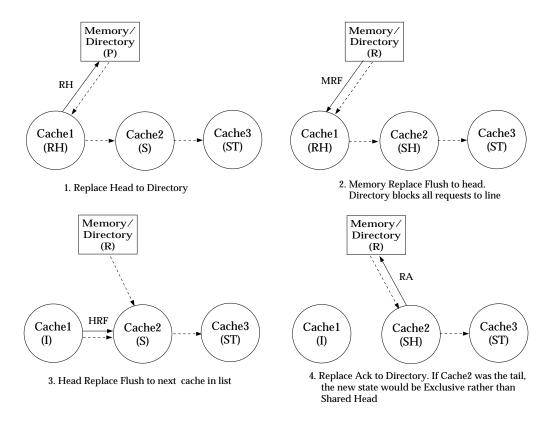

| 3.31 | DD-UP: Replacing Cache Line in Shared Head State         | 69 |

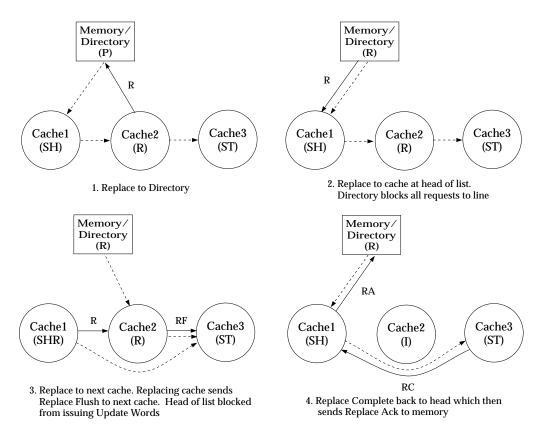

| 3.32 | DD-UP: Replacing Cache Line in <i>Shared</i> State       | 70 |

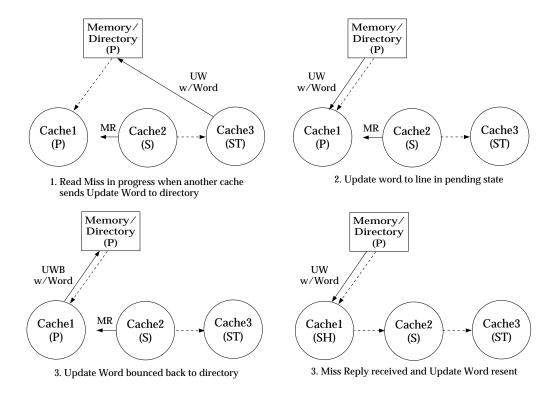

| 3.33 | DD-UP: Race: Update Word to <i>Pending</i> Cache Line    | 71 |

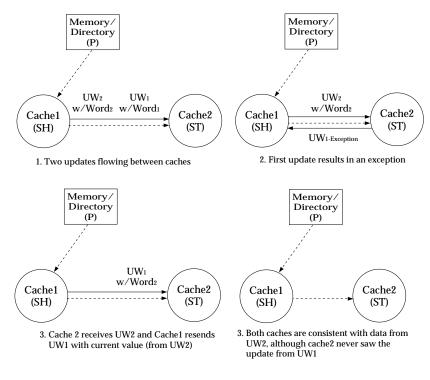

| 3.34 | DD-UP: Update Word Exception                             | 73 |

| 3.35 | Verification Model                                       | 74 |

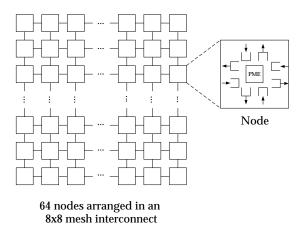

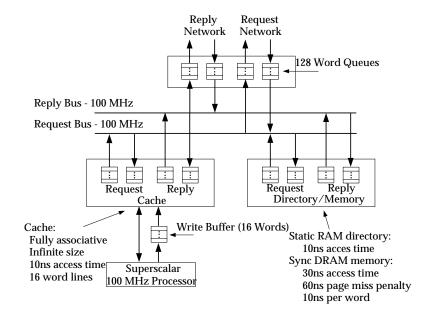

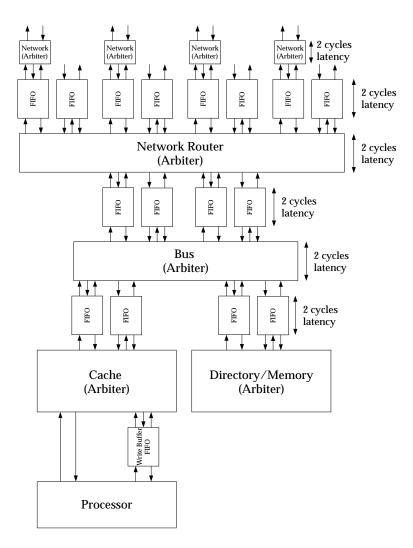

| 4.1  | Network Topology                                         | 78 |

| 4.2  | Processor/Memory Element                                 | 78 |

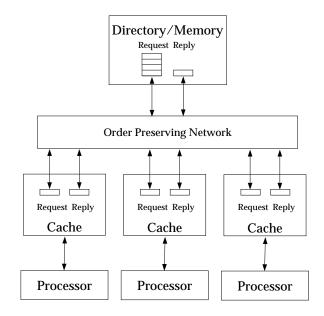

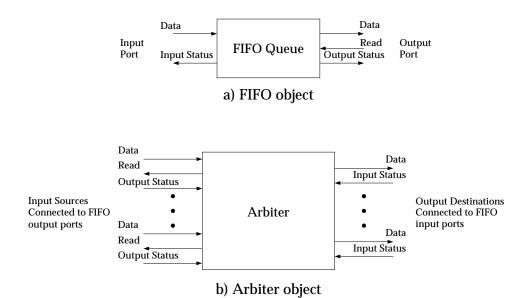

| 4.3  | Basic Simulation Objects                                 | 82 |

| 4.4  | Protocol Source Code Example                             | 84 |

| 4.5  | Simulated PME                                            | 85 |

| 4.6  | Application Domain                                       | 87 |

| 1.0  |                                                          | 01 |

| 5.1  | Block Synchronization                                    | 89 |

| 5.2  | Word Synchronization                                                                    | 90  |  |  |  |

|------|-----------------------------------------------------------------------------------------|-----|--|--|--|

| 5.3  | Block Synchronization and Invalidate-Based Protocols                                    | 92  |  |  |  |

| 5.4  | Block Synchronization and Update-Based Protocols                                        |     |  |  |  |

| 5.5  | Code Examples for Block and Word Synchronization $\ldots \ldots \ldots$                 | 95  |  |  |  |

| 5.6  | Word Synchronization and Invalidate-Based Protocols                                     | 96  |  |  |  |

| 5.7  | Word Synchronization and Update-Based Protocols                                         | 98  |  |  |  |

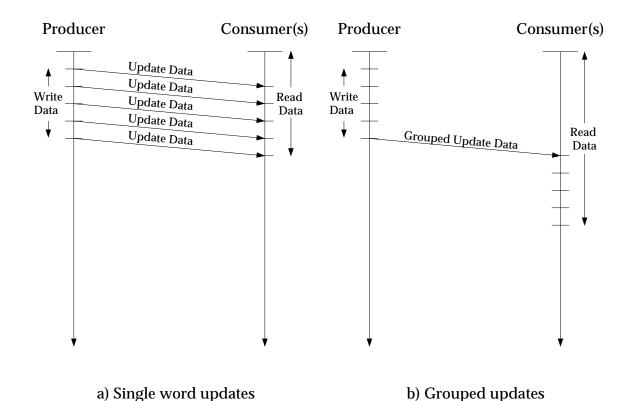

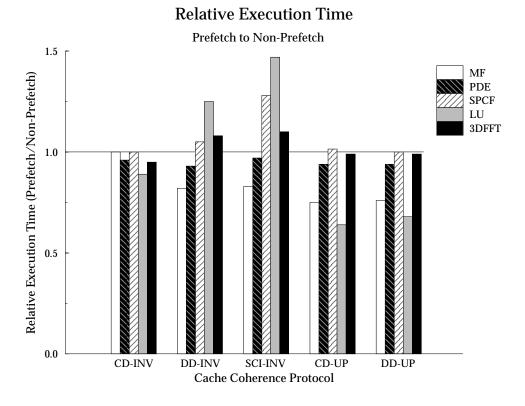

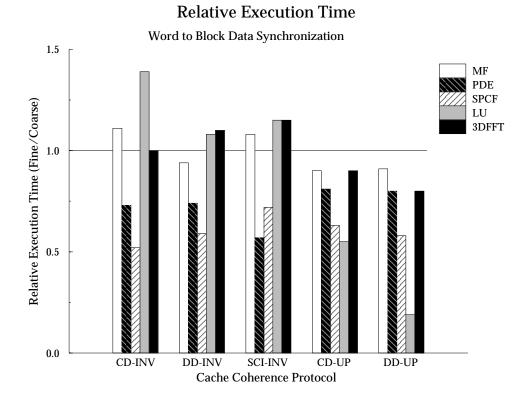

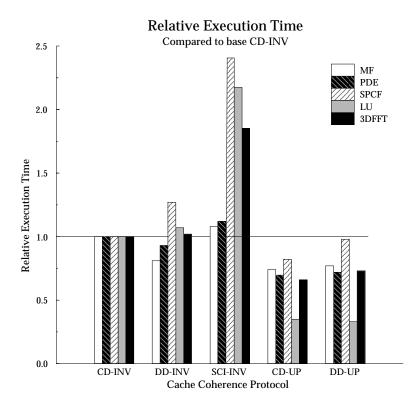

| 5.8  | Relative Execution Time of Applications Using Word Synchronization                      |     |  |  |  |

|      | and Prefetch Compared to the Non-Prefetch Case $\ . \ . \ . \ . \ .$                    | 100 |  |  |  |

| 5.9  | Relative Execution Time of Word Synchronization Compared to Block                       |     |  |  |  |

|      | Synchronization                                                                         | 102 |  |  |  |

| 5.10 | Relative Execution Time of Word Synchronization Compared to a                           |     |  |  |  |

|      | Common Base                                                                             | 106 |  |  |  |

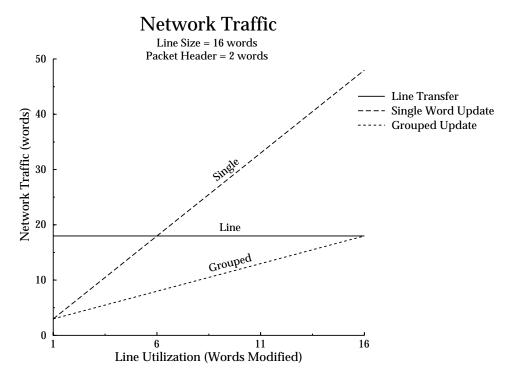

| 5.11 | Network Traffic                                                                         | 108 |  |  |  |

| 5.12 | Software-Based Write Grouping                                                           | 110 |  |  |  |

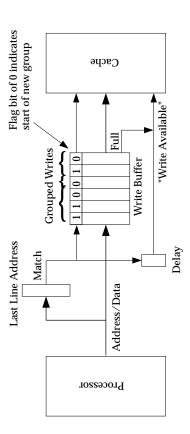

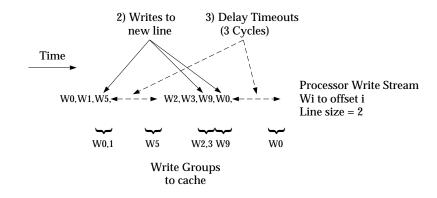

| 5.13 | Hardware-Based Write Grouping at the Write Buffer                                       | 112 |  |  |  |

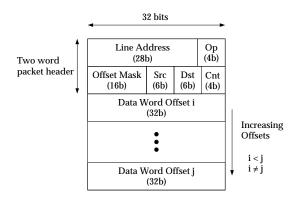

| 5.14 | Hardware-Based Write Grouping Example                                                   | 113 |  |  |  |

| 5.15 | Grouped Update Packet                                                                   | 113 |  |  |  |

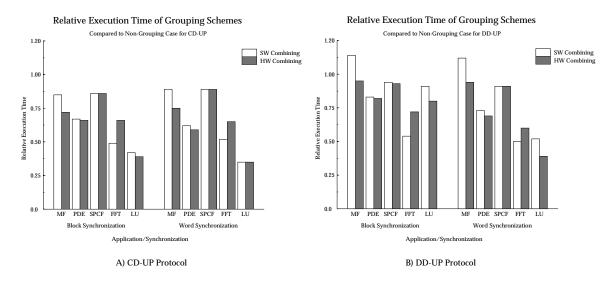

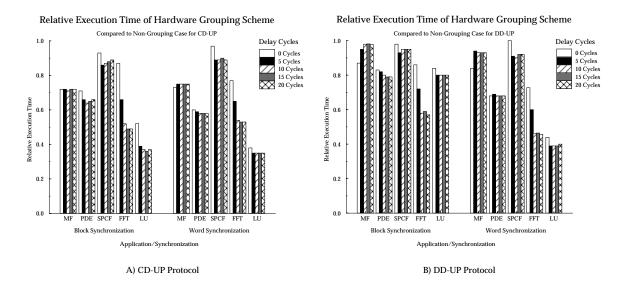

| 5.16 | Relative Execution Time of Grouping Schemes Compared to Non-                            |     |  |  |  |

|      | Grouping Case                                                                           | 116 |  |  |  |

| 5.17 | $Relative \ Execution \ Time \ for \ Alternative \ Grouping \ Delays \ for \ Hardware-$ |     |  |  |  |

|      | Based Grouping                                                                          | 118 |  |  |  |

| 6.1  | Block Synchronization                                                                   | 122 |  |  |  |

| 6.2  | Word Synchronization                                                                    | 123 |  |  |  |

| 6.3  | Relative Execution Time for MF                                                          | 125 |  |  |  |

| 6.4  | Relative Execution Time for PDE                                                         | 127 |  |  |  |

| 6.5  | Relative Execution Time for SPCF                                                        | 129 |  |  |  |

| 6.6  | Relative Execution Time for 3DFFT                                                       | 131 |  |  |  |

| 6.7  | Relative Execution Time for LU                                                          | 132 |  |  |  |

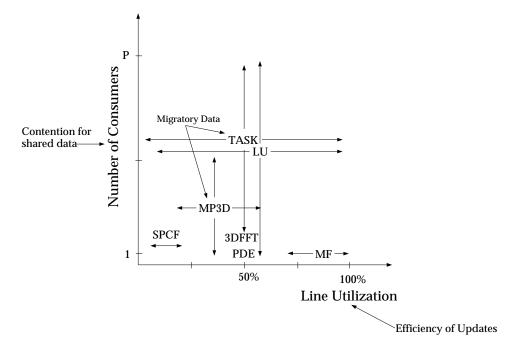

| 6.8  | Application Space                                                                       | 134 |  |  |  |

| 6.9  | Relative Execution Time Averaged Across All Applications                                | 136 |  |  |  |

|      |                                                                                         |     |  |  |  |

| 7.1         | Sensitivity to Cache Access Time                          | 140 |

|-------------|-----------------------------------------------------------|-----|

| 7.2         | Sensitivity to Directory Access Time                      | 142 |

| 7.3         | Sensitivity to Network Bandwidth                          | 143 |

| 7.4         | Sensitivity to Network Latency                            | 145 |

| 7.5         | Sensitivity to Network Multicast                          | 147 |

| 7.6         | Sensitivity to LDST Cycles                                | 148 |

| 7.7         | Relative Execution Time for MP3D                          | 151 |

| 7.8         | Relative Execution Time for TASK Application              | 153 |

| 7.9         | Relative Execution Time for TASK application              | 154 |

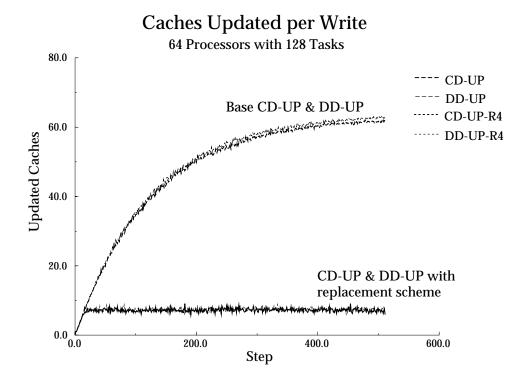

| 7.10        | Cache Updates per Iteration for TASK Application          | 155 |

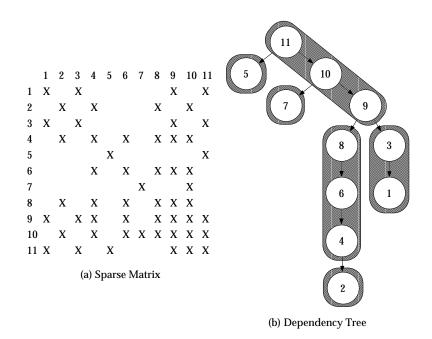

| A.1         | Sparse Matrix and Dependency Tree for Multifrontal Solver | 164 |

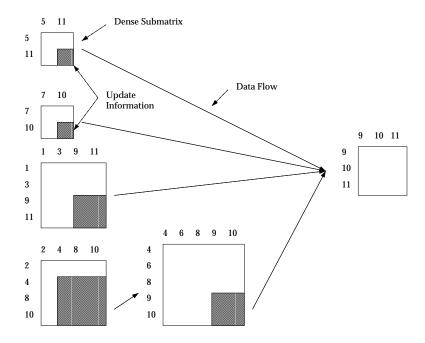

| A.2         | Dense Submatrices and Update Data Flow                    | 165 |

| A.3         | PDE Solver Mesh                                           | 167 |

| A.4         | Data Flow For Cholesky Factorization                      | 169 |

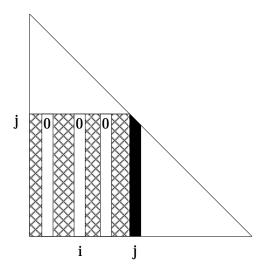

| A.5         | Data Flow for Single Iteration of 3DFFT                   | 172 |

| A.6         | Data Flow For LU Decomposition                            | 174 |

| <b>B</b> .1 | Data Flow For MP3D Decomposition                          | 176 |

## Chapter 1

## Introduction

## **1.1 Parallel Processors**

As the computational requirements for computer applications increase, parallel processors are becoming more popular. Parallel processors attempt to improve the execution time of an application by executing portions of it on separate processors. There are two basic types of parallel processor systems: distributed-memory multicomputers and shared-memory multiprocessors. In distributed-memory multicomputers, independent computer nodes are connected together through a message-passing network. To communicate, nodes send explicit messages between themselves. In sharedmemory multiprocessors, tightly-coupled processors share a global memory space. Communications between processors is implicit in accesses to shared variables. This programming model is preferred by many over the message-passing programming model of the distributed-memory multicomputers as it more closely resembles the programming model used for uniprocessor systems [68].

### **1.2 Shared-Memory Multiprocessors**

Shared-memory multiprocessors may be implemented using one of three models: the uniform memory access (UMA) model, the non-uniform memory access (NUMA) model, or the cache-only memory (COMA) architecture [40, 47, 25]. Discussion of

the COMA architectures is beyond the scope of this dissertation.

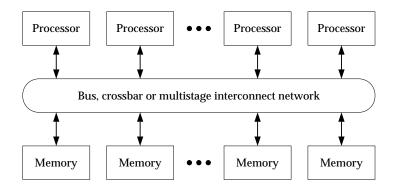

In the UMA model, each processor has an uniform memory access latency for each word of memory. The processors may be connected to the memory by a shared bus, crossbar switch or multistage interconnect network, as shown in figure 1.1. One disadvantage of the UMA model is that as the size of the system is scaled up, the memory access latency of *all* memory increases.

Figure 1.1: Uniform Memory Access (UMA) Model

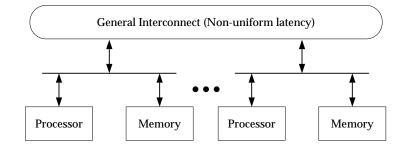

The NUMA model addresses the scalability issue by physically distributing memory among the processors, as shown in figure 1.2. In this case, the latency of a memory access is dependent on the physical location of memory. The local memory access latency is constant regardless of the size of the system, but the non-local or remote memory access latency varies based on the distance from the requesting processor to the remote memory. Several techniques have been presented to tolerate or reduce this memory access latency, which may become significant for remote memory accesses. These include processor caches [64], relaxed memory consistency models [1, 22, 38, 33] and software-controlled data prefetch [55]. The remainder of this chapter describes the problem introduced by processor caches in shared-memory multiprocessors, and chapter 2 describes the relaxed memory consistency models and software-controlled data prefetch in greater detail.

Figure 1.2: Non-Uniform Memory Access (NUMA) Model

### **1.3** Cache Coherence

A processor cache is a small, fast memory placed near the processor that holds the most recently accessed data [64]. When the desired data is not found in the cache, a cache miss occurs and the data is fetched from the memory and placed in the cache. The addition of these caches to shared-memory multiprocessors introduces a data consistency problem known as the cache coherence problem<sup>1</sup>.

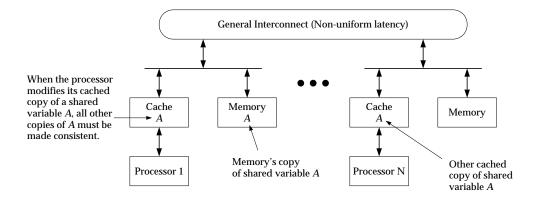

The problem is that a given memory line may be present in any of the processor caches. To execute programs correctly<sup>2</sup>, the copies of this memory line must remain consistent. Therefore, when a processor modifies its cached copy of the line, other caches that have a copy of the line must be notified so that their copy may be made consistent.

For example, in figure 1.3 the shared variable A is being shared by multiple processors. When processor 1 modifies its cached copy of A, the other remote cached copies must be made consistent and memory's copy may need to be made consistent.

<sup>&</sup>lt;sup>1</sup>The terms coherence and consistency tend to be used interchangeably in the literature.

<sup>&</sup>lt;sup>2</sup>Some iterative programs may still converge even if memory is not always coherent.

Figure 1.3: Cache Coherence Problem

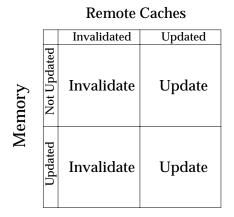

The two methods for maintaining consistency on a write are invalidating or updating the remote copies of the memory line. Invalidating purges the copies of the line from the other remote caches which results in a single copy of the line in the writing processor's cache, and updating forwards the write value to the other remote caches, after which all caches are consistent. This consistency of data is maintained through what is known as a cache coherence protocol.

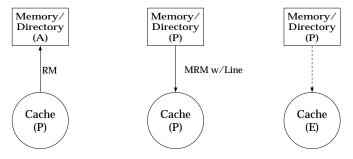

Cache coherence protocols define what actions are required when a processor modifies a cached copy of a memory line. The protocols must guarantee that after the actions triggered by the write are completed, all caches in the system are consistent with each other. Figure 1.4 summarizes the possibilities that result from either invalidating or updating the remote caches and possibly updating memory. These four possibilities result in two classes of protocols: update-based (UP) or invalidate-based (INV). For update-based protocols, remote caches are updated on a write, and memory may be updated on every write. For invalidate-based protocols, remote caches are invalidated and memory may be updated when a writing cache releases exclusive ownership of the line. All protocols update memory's copy of a line if memory is not consistent when the last cached copy of the line is replaced.

Figure 1.4: Protocol Classes

The details of the cache coherence protocols are dependent on the structure of the underlying interconnect. If all caches and memories are connected to a common bus, a broadcast-based protocol may be used, but if a general interconnect is used in which caches cannot observe all memory transactions, a directory-based protocol is necessary [66].

#### **1.3.1** Broadcast-Based Protocols

Broadcast-based protocols rely on the ability of each cache to observe or "snoop" all memory transactions on the shared bus and change the state of the cache lines appropriately [8]. Each cache operates independently of all other caches. If a cache observes a write to a memory line it has a copy of, the cache coherence protocol will either invalidate or update the cached copy depending on the type of protocol used.

Several broadcast-based protocols have been specified in the literature. These include both invalidate-based and update-based protocols. The invalidate-based protocols include Goodman's write-once [37], the Synapse [30], the Illinois [58] and the Berkeley [29] protocols. The update-based protocols include the Firefly [67] and the Dragon [54] protocols. These protocols have been well studied [46, 26, 8, 7, 54, 67].

The next two sections give a brief description of how the Berkeley invalidatebased protocol and the Dragon update-based broadcast protocols operate for typical processor reads and writes.

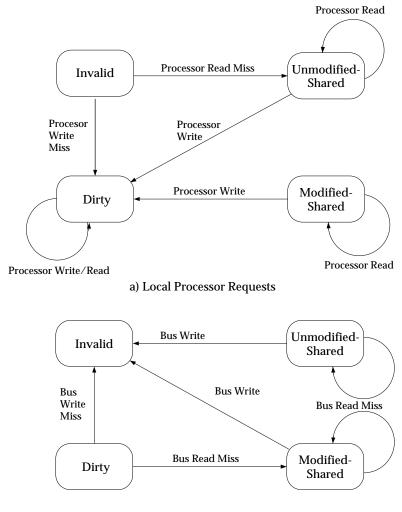

#### Berkeley Invalidate-Based Protocol

In the Berkeley invalidate-based protocol, a cache line may be in one of four states:

- Invalid Cached copy of line is not valid,

- Unmodified-Shared Read only copy of line and memory is consistent,

- Modified-Shared Read only copy of line and memory is not consistent, or

- Dirty Read/Write copy of line and memory is not consistent.

Figure 1.5 shows the state diagrams for the protocol. The state of a cache line may change as a result of a local processor request or an observed memory transaction by another processor, as shown in figure 1.5a and 1.5b respectively.

On a processor read miss, the state of the cache line is set to UnModified-Shared, and if another cache has a copy of the line, then it supplies the data and changes its local state appropriately.

On a processor write miss or a write hit to a read-only line, the state is set to Dirty. All other copies of the line are invalidated, as the other caches observe the write on the bus. If the line was owned by another cache, the owning cache supplies the data and invalidates it copy.

The protocol has several important characteristics. First, exclusive ownership of the line (Dirty state) is required before the line can be modified. Second, cache-tocache transfers are used when possible to satisfy miss requests. This reduces the need for expensive accesses to main memory, and third, main memory is only updated when a dirty cache line is replaced by the owning cache.

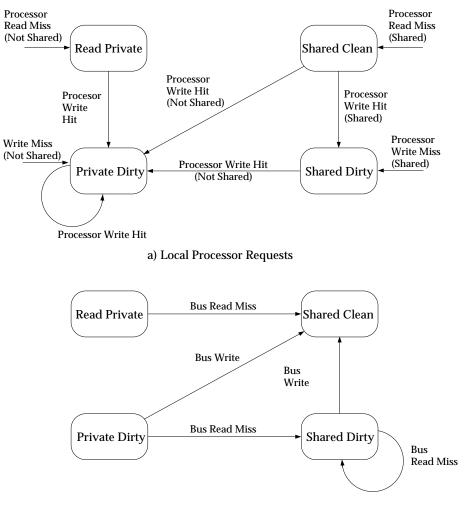

#### Dragon Update-Based Protocol

In the Dragon update-based protocol a cache line may be in one of five states:

- Invalid Cached copy of line is not valid,

- Read-Private Only copy of line and memory is consistent,

- Private-Dirty Only copy of line and memory is not consistent,

b) Bus Requests (Remote Processor Requests)

Figure 1.5: Berkeley Invalidate-Based Cache Coherence Broadcast Protocol

- Shared-Clean Multiple copies of line and memory is consistent, or

- Shared-Dirty Multiple copies of line and memory is not consistent.

Figure 1.6 shows the state diagrams for the Dragon update-based cache coherence protocol. As in the Berkeley protocol, the state may change as a result of a processor access or an observed memory transaction. The protocol uses a special sharing line that is asserted if at least one other cache has a copy of an accessed line.

On a read miss, the local cache line state is set to either Read-Private if no other shared copies of the line exist or to Shared-Clean if the sharing line is asserted during the miss. If one of the caches has the line in the Private-Dirty state, then that cache supplies the data for the miss and sets the cache line state to Shared-Dirty. If one of the caches is already in the Shared-Dirty state, it simply supplies the data for the miss. If one of the caches has the line in the Read-Private state, it supplies the data for the miss and sets the cache line state to Shared-Clean.

On a write miss, all other copies of the line must be updated. The cache line state is set to Private-Dirty if there are no other shared copies of the line, or it is set to Shared-Dirty if other copies do exist. All caches with a copy of the line update their copy and set the cache line state Shared-Clean. If a cache was in the Private-Dirty state, it supplies the data for the miss. Memory's copy is no longer valid. When the last Shared-Dirty copy is replaced, memory is updated.

For this protocol, exclusive ownership of the line is not required to modify the line, but the protocol does requires the special sharing line. There can be multiple writers of a line unlike the invalidate-based Berkeley protocol. The protocol also uses cache-to-cache transfers.

Several studies have indicated that there is little performance difference between broadcast-based cache coherence protocols which maintain consistency through invalidations or updates [27, 46].

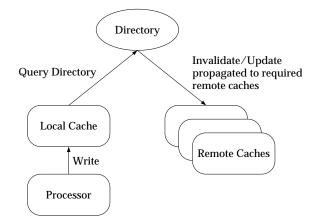

#### **1.3.2** Directory-Based Protocols

The main problem with broadcast-based protocols is that they rely on an interconnect that allows broadcasts of all memory transactions. Interconnects such as buses do not

b) Bus Requests (Remote Processor Requests)

Figure 1.6: Dragon Update-Based Cache Coherence Broadcast Protocol

Figure 1.7: Directory-Based Cache Coherence Protocols

scale well as the shared bus saturates after a small number of processors are attached to it [68]. A scalable system is one in which the performance of the system increases linearly with the size of the system. To build such a scalable system, other interconnects that scale better are required. These interconnects, such as two-dimensional meshes, do not allow caches to observe or "snoop" all other memory transactions.

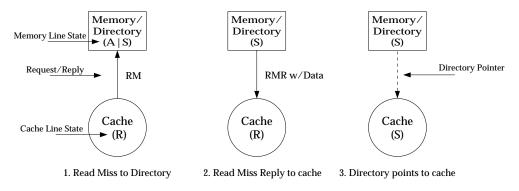

This change in the network structure imposes two new requirements on the cache coherence protocols [66]. First, the protocols must now explicitly notify other caches when a cache line has been modified. To send these notifications, the protocols must be able to send and receive protocol level messages. The second requirement is that a logical list of caches holding a copy of each memory line must be maintained so that each write notification may be sent only to the caches which have a copy of the line. This list of caches holding a copy of each line is stored in what is known as a "directory". The directory may be physically implemented in several ways as will be described in section 3.1, but each directory entry will logically maintain a list of caches holding a copy of the respective memory line.

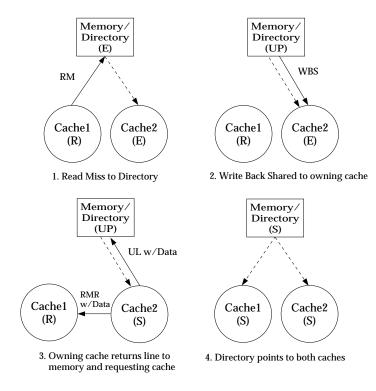

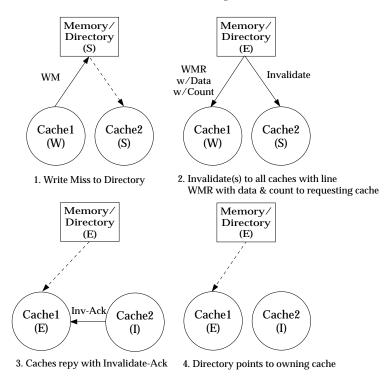

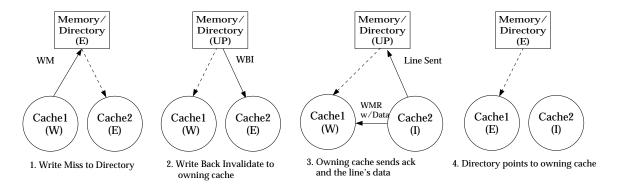

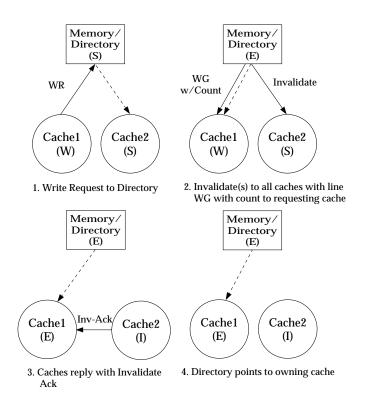

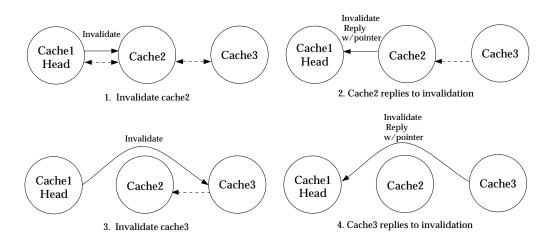

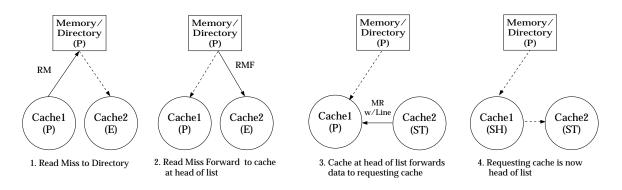

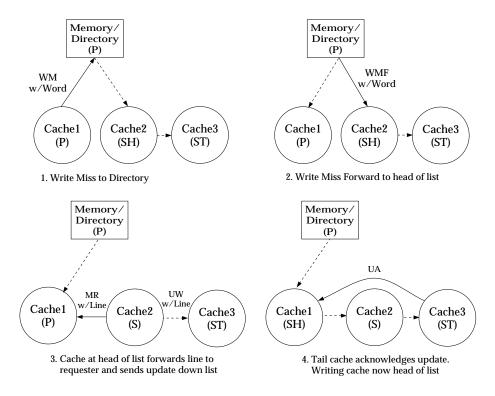

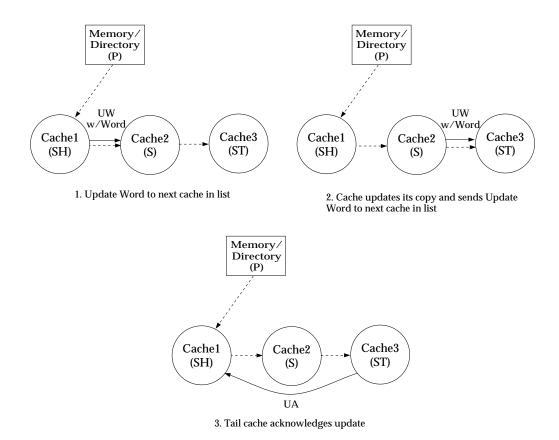

The directory-based cache coherence protocols use the directory entry to forward write information to the necessary caches. Figure 1.7 shows the basic operations for a directory-based protocol. When a cache receives a write request from the processor, it must query the directory to determine which caches must be invalidated or updated for invalidate-based or update-based protocols respectively. Once all the caches have received and processed the invalidation or update, all caches in the system are consistent. Section 3.3 will describe three different implementations of invalidate-based protocols presented in the literature, and section 3.4 will present two new update-based protocols. The remainder of this dissertation examines the performance difference between these two classes of directory-based cache coherence protocols.

### **1.4** Organization of Dissertation

This dissertation is organized as follows. First, chapter 2 reviews two techniques for reducing and tolerating memory access latency. These are relaxed memory consistency models and software-controlled data prefetch. Chapter 3 reviews three invalidatebased protocols described in the literature and describes two new update-based protocols. Validation of the update-based protocols is discussed. Chapter 4 describes the methodology used in this dissertation to compare the performance of the cache coherence protocols. This includes a description of the simulation environment, the multiprocessor architecture, and the application space. Next, chapter 5 presents two additional techniques that can be applied to update-based protocols to reduce and tolerate memory access latencies. These include a word synchronization scheme and a write grouping scheme. Next, chapter 6 presents the simulated performance of the protocols studied, and chapter 7 examines the sensitivity of the protocol's performance to variations in architectural parameters and to applications with migratory data. Finally, chapter 8 concludes the dissertation by comparing and contrasting the protocol classes in terms of their correctness, cost and efficiency of maintaining the desired memory consistency model.

## 1.5 Contributions of Dissertation

The main contribution of this dissertation is the development and analysis of updatebased cache coherence protocols for scalable shared-memory multiprocessors. It designs and validates two update-based protocols based on a centralized directory and a distributed directory. The work analyzes the performance of the update protocols and identifies the two fundamental limitations of the update-based protocols: the inefficiency of single word updates and the mismatch between the coarse granularity of the data synchronization and the fine granularity of the data updates. Two techniques are presented to overcome these limitations. The first, a write grouping scheme, is used to improve the efficiency of the updates; the second, a finer grain (word) data synchronization scheme, is used to provide a better match between the granularity of the data synchronization and data updates.

The dissertation compares the performance of the update-based protocols to three high performance invalidate-based protocols presented in the literature. The simulations demonstrate the limitations of the update-based protocols and how the two techniques, write grouping and word synchronization, improve the performance of the update-based cache coherence protocols.

The sensitivity of the protocols to architectural parameters is examined. And, finally, the problem of migratory shared data and update-based protocols is discussed, and a technique to limit the performance loss due to the unnecessary updating of migratory data is presented.

Overall, the dissertation demonstrates that update-based protocols can be designed to significantly improve the performance of fine-grain scientific applications.

## Chapter 2

# Latency Reducing and Tolerating Techniques

There are several techniques that can be used to either reduce or tolerate memory access latency. These techniques, which were briefly introduced in the last chapter, include processor caches, relaxed memory consistency models and software-controlled data prefetch. The last chapter described the cache coherence problem introduced by the addition of processor caches to shared-memory multiprocessor systems. In this chapter, relaxed memory consistency models and software-controlled data prefetch are described, and their impact on the cache coherence protocols is examined.

### 2.1 Memory Consistency Models

Memory consistency models describe the ordering of memory access events as seen by the programmer. Censier and Feautrier [12] define memory system coherence as follows

**Definition 2.1** A memory scheme is *coherent* if the value returned on a load instruction is always the value given by the latest store instruction with the same address.

The problem with this definition is that the meaning of "latest store" is unclear. To make the definition of memory consistency more precise, several memory consistency models have been defined in the literature. These include sequential consistency [52], processor consistency [38], weak consistency [22] and release consistency [33].

Dubois and Scheurich [21] have defined several terms required to properly define a memory consistency model. The terms define the ordering of memory access events. These events may be a memory load or store if the type is not specified.

**Definition 2.2** Initiated memory request: A memory access is initiated when a processor has sent the request and the completion of the request is out of its control.

**Definition 2.3** *Issued memory request:* An initiated request is *issued* when it has left the processor environment and is in transit in the memory system.

**Definition 2.4** *Performed load:* A load is considered *performed* at a point in time when the issuing of a store to the same address cannot affect the value returned by the load.

**Definition 2.5** Performed store: A store to address X by processor i is considered performed at a point in time when an issued load to the same address returns the value defined by a store in the sequence Si(X)+.

The sequence Si(X)+ refers to the stream of stores to address X from processor i. From definition 2.5, the store is complete when a load returns the value of the store or the value of any subsequently performed store.

In systems with atomic memory accesses, a memory access is performed with respect to all processors at the same time. In systems where a store may be performed at different processors at different times a further refinement of the definition of performed is required.

**Definition 2.6** Performed load with respect to processor k: A load is considered performed with respect to processor k at a point in time when the issuing of a store to the same address by processor k cannot affect the value returned by the load.

**Definition 2.7** Performed store with respect to processor k: A store to address X by processor i is considered performed with respect to processor k at a point in time when an issued load to the same address by processor k returns the value defined by a store in the sequence Si(X)+.

For non-atomic memory systems, the definition of *performed* is now given by

**Definition 2.8** *Performed store:* A store is *performed* when it is performed with respect to all processors.

**Definition 2.9** Globally Performed load: A load is globally performed when it is performed with respect to all processors and if the store which is the source of the returned value is globally performed.

For systems with a write buffer, the definitions must be slightly modified [32].

**Definition 2.10** Performed store with respect to processor k (with write buffering): A store by processor i eventually performs with respect to processor i. If a load by processor i performs before the last store (in program order) to the same address by processor i performs with respect to processor i, then the load returns the value defined by that store. Otherwise, the load returns the value defined by the last store to the same address (by any processor) that performed with respect to processor i(before the load performs). A store is *performed* when it is performed with respect to all processors.

This new definition is required since a load request may find the desired data in the write buffer and, therefore, be performed without querying the cache or interacting with the coherence mechanism.

With these definitions, several different memory consistency models can now be presented. These include sequential consistency, processor consistency, weak consistency and release consistency. The models vary on how strongly ordered the memory accesses are. Sequential consistency requires the ordering of accesses from all processors. The other consistency models, known collectively as relaxed consistency models, relax this total ordering and only specify the order of accesses by individual processors.

#### 2.1.1 Sequential Consistency Model

Lamport [52] has defined a sequential consistency model as

**Definition 2.11** A system is *sequentially consistent* if the results of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program.

In a sequentially consistent multiprocessor, memory accesses appear to execute atomically in some total order [51]. To a programmer, a sequentially consistent multiprocessor would be indistinguishable from a multitasking uniprocessor.

Scheurich and Dubois [21] have described a set of sufficient conditions for sequential consistency. The conditions, slightly modified and combined [69], are

**Condition 2.1** Sufficient conditions for sequential consistency: Before a load or store access is allowed to perform with respect to any processor, all previous load accesses must be globally performed and all previous stores must be performed.

#### Implementation

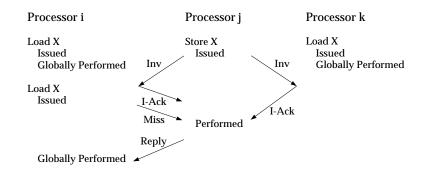

For invalidate-based protocols, these conditions may be satisfied by delaying the issuing of a memory access from processor i until all previous memory accesses issued by this processor have been performed. With this constraint, load accesses by different processors are not ordered, but the stores to the same address are, and the stores are also ordered with respect to the loads. The invalidation mechanism provides for this store ordering. When a store to address X is issued by processor i, other processors may still globally perform loads from this address. But once the store is performed with respect to processor j, any load from address X issued by processor j cannot be globally performed until the store issued by processor i has been performed.

This ordering of stores is possible in the invalidate-based protocols since the processor issuing the store, processor i, obtains exclusive ownership of the line. Any load request for this line is blocked by processor i until the store has been performed (all invalidations have been acknowledged). For example, figure 2.1 shows a sequence of loads and stores for three processors. First, processor i and k issue a load from address X and processor j issues a store to address X. The loads can be globally performed since the store has not yet been performed with respect to either processor i or k.

#### 2.1. MEMORY CONSISTENCY MODELS

Once the invalidation request reaches processor i, the store is considered performed with respect to processor i. The next load from address X issued by processor i is now blocked by processor j since the pending store has not yet been performed (all invalidations acknowledged). Once the invalidation has reached processor k and both processor i and k acknowledge the invalidation, the store is considered performed, and the blocked load of processor i can be globally performed.

Figure 2.1: Sequential Consistency - Invalidate-Based Protocols

The ordering of accesses to a given line is determined by the relative timing of the invalidation request. If a load is issued by processor i before a store from processor j has been performed with respect to processor i, the load will appear as if it was performed before the store in the total ordering. If the load by processor i is issued after the store is performed with respect to processor i then the load will appear as if it occurred after the store in the total ordering. The invalidation mechanism allows for the ordering of loads with respect to stores.

For update-based protocols, neither the loads nor stores are ordered. This lack of ordering for the stores creates a significant problem for update-based protocols attempting to implement a sequential consistency model. To implement such a model, the update-based protocols must be augmented with a mechanism that will allow for the ordering of stores. Wilson and LaRowe [72] have demonstrated how a two-phase update would allow for this proper ordering of stores.

The example shown in figure 2.2a, taken from Wilson and LaRowe [72], demonstrates how an update-based protocol may violate sequential consistency even if a processor delays all memory accesses until all previous memory accesses from the

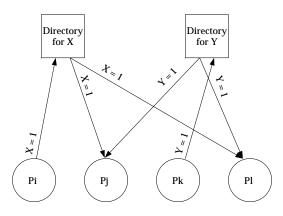

| Processor i | Processor j                             | Processor k | Processor l                             |

|-------------|-----------------------------------------|-------------|-----------------------------------------|

| x = 1;      | while (x != 1);<br>print y;<br>print y; | y = 1;      | while (y != 1);<br>print x;<br>print x; |

x and y are initially 0

a) Code example

b) Update flow

Figure 2.2: Violating Sequential Consistency - Update-Based Protocols

same processor have been performed. This requirement was sufficient for invalidatebased protocols to provide sequential consistency.

In the example, processors i and k write to two control variable X and Y respectively. If the system is sequentially consistent, such as with a uniprocessor, then either both processors print two ones, one processor prints a zero followed by a one and the other prints two ones, or one processor prints two zeros and the other prints two ones. If both processors print a zero followed by a one, then sequential consistency has been violated. This ordering may occur in an update-based protocol if the directories for the two variable, X and Y, are located at different nodes. In this case, the path of the updates will differ and the stores to X and Y may be performed with respect to processors j and l in a different order, as shown in figure 2.2b. This case violates the condition that an issued store be performed before any other memory accesses may be issued.

#### 2.1. MEMORY CONSISTENCY MODELS

The problem arises because when a store is performed with respect to processor i, the processor obtains the new value of the store. Other processors to which the store has not yet been performed are still able to access the old value. As in the invalidate-based protocols, the load performed at processor j prior to the store being performed at processor j simply appears prior to the store in the total ordering. The problem is that the processors to which the store has been performed with respect to can issue a load which will be performed before the store has been performed. This problem is prevented in invalidate-based protocols since the writing cache controls when the loads can be performed.

A two-phase update prevents this scenario by issuing a store to address X in two phases. The first phase of the store informs each cache with a copy of the line containing X that an update has been issued. These caches would not allow their respective processors to perform accesses to this address. After the first phase of the update has been performed with respect to all processors, the second phase of the update sends the actual data to the appropriate caches. Once cache *i* receives this update, processor *i* is able to perform loads from address X. This scheme prevents processor *i* from performing a load of the new value from address X while processor *j* may load an old value.

#### 2.1.2 Processor Consistency Model

To improve system performance, the memory consistency model may be relaxed. The first of such relaxed memory consistency models is the processor consistency model defined by Goodman [38]. Goodman gives the conditions for processor consistency as

**Condition 2.2** Conditions for processor consistency: Before a load is issued by a processor, all previous load accesses by that processor must be performed. Before a store is issued by a processor, all previous memory accesses by that processor must be performed.

Processor consistency requires that stores from a processor be performed with respect to all processors in the same order, but stores from different processors are not ordered. The condition also allows for reads to bypass writes and, therefore, the introduction of a write buffer, but stores may only be retired from the write buffer after they have been performed [31]. This retirement constraint limits the number of outstanding stores per processor to one.

#### Implementation

For both classes of protocols, implementing processor consistency is not difficult. Since loads are able to bypass stores, the processor may simply issue a load and stall until the load has been performed. For the stores, the processor issues the store to the write buffer (stalls if write buffer is full) and continues execution. As noted above, the stores cannot be retired (removed) from the write buffer until the store has been performed. This retirement constraint guarantees ordering of stores since each processor can have at most one issued, but not yet performed store.

#### 2.1.3 Weak Consistency Model

The next progression in memory consistency models is a weak consistency model [22]. In weak consistency, accesses are divided into either synchronization accesses or normal accesses. These accesses are defined as [69]

**Definition 2.12** Synchronization access: An access is a synchronization access if it is used to order events. For example, a synchronization flag can be used to order the accesses to a block of data by a producer and consumer, or a lock can be used to order process accesses to a critical section of code.

**Definition 2.13** Normal access: An access is a normal access if it is not used to order events. These accesses include simple loads and stores.

If the synchronization events are identified by the programmer or compiler, then the caches and memory must be consistent only at these synchronization points.

Dubois, et al [21] proposed a weak consistency model and presented conditions for weak consistency (as slightly modified by Gharachorloo [31])

**Condition 2.3** Conditions for weak consistency: Before a normal access is allowed to perform with respect to any other processor, all previous synchronization accesses

must be performed, and before a *synchronization* access is allowed to perform with respect to any other processor, all previous *normal* accesses must be performed. *Synchronization* accesses are sequentially consistent with respect to one another.

### Implementation

For both classes of protocols, the weak consistency model introduces the need for a fence instruction. A fence instruction stalls the processor until all previous synchronization and normal accesses have been performed. Thus, hardware counters are required to keep track of outstanding accesses. For invalidate-based protocols, these accesses include outstanding write misses and unacknowledged invalidation requests, and similarly for update-based protocols, they include outstanding write misses and unacknowledged write updates. When a processor issues a fence instruction, the processor is stalled until all counters are zero, which indicates that all writes have been performed.

In weak consistency, the burden of synchronization is placed on the compiler and programmer. It is their responsibility to place synchronization accesses at the proper locations in the code to protect critical regions and guarantee correct access order to shared data. Fence instructions are requires around synchronization accesses to satisfy condition 2.3.

## 2.1.4 Release Consistency Model

The final memory consistency model discussed in this dissertation is the release consistency model [33]. In this model, the conditions of weak consistency are relaxed even further. Release consistency divides memory accesses into two major categories: competing and normal. Two accesses are competing if they are to the same memory location and at least one access is a store. The competing accesses are further divided into synchronization accesses and non-synchronization accesses. The synchronization accesses are used to order events and are divided into acquire or release accesses. These synchronization accesses are defined by Gharachorloo, *et al* [33] as **Definition 2.14** An *acquire* synchronization access (e.g., a lock operation or a process spinning for a flag to be set) is performed to gain access to a set of shared locations.

**Definition 2.15** A *release* synchronization access (e.g., an unlock operation or a process setting a flag) grants permission to access a set of shared locations.

Note that an acquire is a load operation and a release is a store operation.

In weak consistency, processors must wait for a synchronization event to be performed before continuing. Release consistency relaxes the consistency model by noting that a process performing a release access does not need to wait for the release's store operation to be performed and that a process performing an acquire access does not need to wait for previous accesses to be performed. The conditions for release consistency are given by Gharachorloo, *et al* [33] as

**Definition 2.16** Conditions for release consistency: Before a normal access is allowed to perform with respect to any other processor, all previous acquire accesses must be performed, and before a release access is allowed to perform with respect to any other processor, all previous normal accesses must be performed. Acquire and release accesses are processor consistent with respect to one another.

## Implementation

As with weak consistency, hardware counters are also required to keep track of outstanding accesses [33]. Again, the burden is placed on the programmer and compiler to insert synchronization accesses and fence instructions at the proper locations in the code, but the release consistency model requires fewer fence operations than the weak consistency memory model.

## 2.1.5 Summary

In this section four memory consistency models were described. The strongest model, sequential consistency, requires that all memory accesses appear atomic. This requirement presents difficulties for update-based protocols, but a two-phase update-based

protocol can be used to implement sequential consistency. Relaxed consistency models were introduced to improve system performance. The relaxed consistency models allow more overlap of memory accesses. This overlap effectively reduces the memory access latency by hiding it behind other useful work. The first relaxed consistency model, processor consistency, required that stores from a given processor be performed with respect to all other processors in the same order as they were issued. Weak consistency and release consistency divide accesses into normal load and store accesses and synchronization accesses and only require memory and caches to be consistent at the synchronization points. Release consistency goes further by dividing synchronization accesses into acquire and releases and relaxes the ordering of these accesses. In the remainder of this dissertation, the applications studied will use a release consistency memory model.

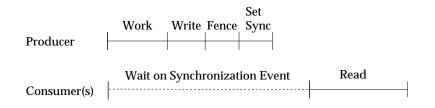

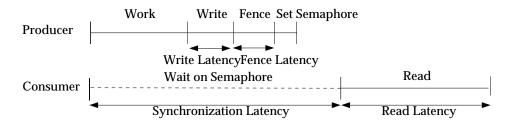

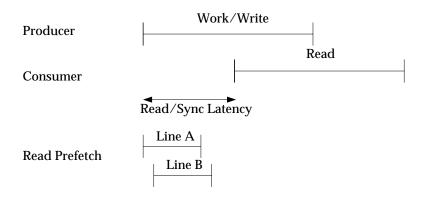

# 2.2 Software-Controlled Data Prefetch

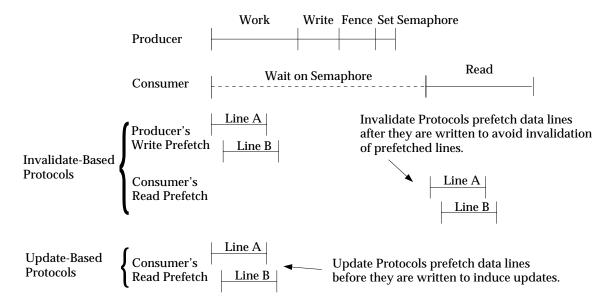

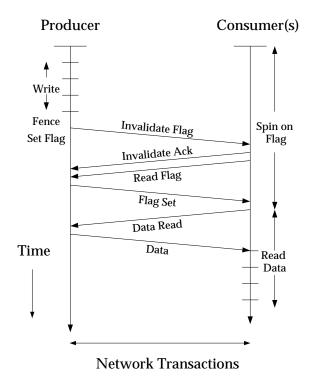

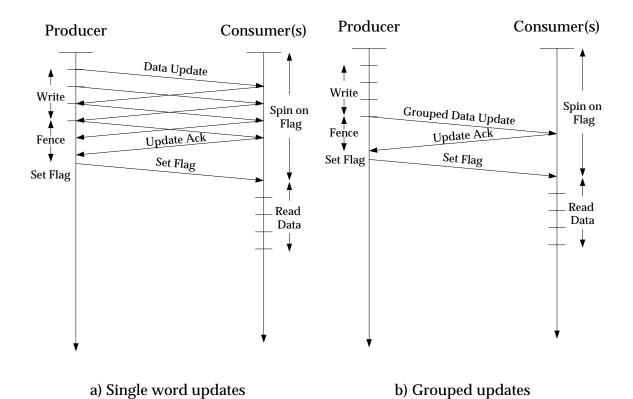

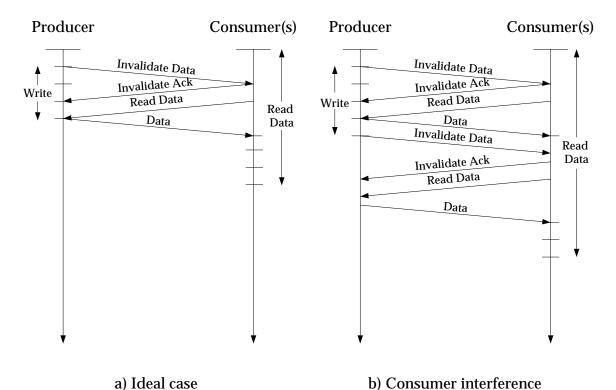

Another technique to reduce the memory access latency is software-controlled, nonbinding data prefetch [55]. The data prefetch moves the requested data to the cache nearest the processor. This data prefetch can be used to hide a portion of the data miss latency in a typical producer and consumer interaction [55], as shown in figure 2.3. In the figure, the producer and consumer share a block of data using a release consistency memory model or what will be referred to as block synchronization throughout the remainder of this dissertation. The producer computes the data, writes the results to a shared buffer, and then uses a fence instruction to stall the processor until all writes have been performed. Once the writes have been performed, the semaphore is set. Consuming nodes wait for the semaphore to be set before attempting to access the shared data.

In the invalidate-based protocols, a write prefetch (or exclusive read) can be used to hide a portion of the producer's fence latency by issuing write requests early and overlapping multiple requests, as shown in figure 2.3. The write prefetch allows the write miss and fence latency to be overlapped with useful work.

Figure 2.3: Block Synchronization with Prefetch

A read prefetch can also be used to reduce the consumer's read miss latency in an invalidate-based system, but the prefetches should be issued after reaching the synchronization point. If the prefetches are issued earlier, two scenarios are possible. In the first case, the producer has not yet written the data. In this case, the prefetched lines will be later invalidated, and the work done to prefetch and invalidate the lines will be wasted. In the second case, the producer has completed writing the data before the consumer's prefetch is received. In this case, the prefetch will obtain the proper data, but the time saved compared to prefetching after the synchronization point will be minimal since the producer would have also set the semaphore and the consumer's read of the semaphore would have found it set. The latency saved by prefetching early is small compared to the high cost of invalidated prefetches. For the invalidate-based protocols and the applications examined in this dissertation, prefetching before the synchronization point never resulted in a faster execution time than prefetching after the synchronization point for the invalidate protocols.

In the update-based protocols, read prefetches can be used not only to hide read miss latency behind useful work, but they also can be used to induce updates. If the prefetch is issued before the data is written by the producer, the consumer's cache will be updated when the data is written. The prefetch allows the consumers to express an early interest in the data.

# 2.3 Summary

This chapter reviewed two techniques to reduce and tolerate memory access latency. The first, relaxed memory consistency models, relaxed the ordering of accesses. This technique allowed for more overlap of memory accesses and, therefore, a reduction in memory access latency. The second technique, software-controlled data prefetch, allowed miss latency to be tolerated by overlapping miss requests with useful work or other miss requests. Prefetch also has an important role in update-based cache coherence protocols; it allows the consumers of data to express an early interest in a piece of data. If the consumers prefetch the data, then when it is written by the producer, the consumer's cache will be updated. Chapter 5 presents two other techniques that can be used with update-based protocols to help reduce and tolerate memory access latency.

# Chapter 3

# **Directory-Based Protocols**

This chapter describes the directory-based cache coherence protocols studied in this dissertation. First, section 3.1 reviews the directory structures required by the protocols, and section 3.2 describes protocol level deadlock. Next, section 3.3 briefly reviews three invalidate-based protocols presented in the literature, and section 3.4 presents two new update-based protocols. In particular, section 3.4.1 describes a centralized directory update-based protocol and section 3.4.2 describes a singly-linked distributed directory update-based protocol. Finally, section 3.5 discusses validation of the update-based protocols using an exhaustive validation tool called Mur $\varphi$  [19].

# 3.1 Directory Structures

Directory-based cache coherence protocols must maintain a directory entry for each memory line in the system. This directory entry indicates which caches in the system have a copy of the respective memory line. Each directory entry can be stored in a single, central location (centralized directory protocol) or distributed among the caches holding a copy of the line (distributed directory protocol). In both cases, the directory entries are distributed throughout the system with their respective memory lines.

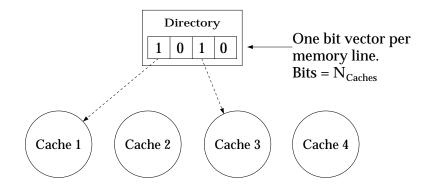

## 3.1.1 Centralized Directory

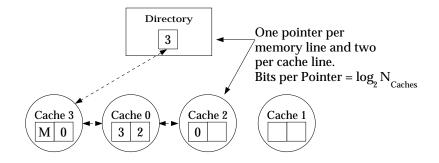

In a centralized directory (CD) protocol, each directory entry contains a pointer to each cache in the system that contains a copy of the respective memory line. In the CD protocols studied in this work, a fully mapped directory is used in which there is a single bit pointer for each cache in the system [66]. For example, figure 3.1 shows a directory entry for a memory line in a four cache system. In the example, caches 1 and 3 have a copy of the given memory line.

Figure 3.1: Centralized Directory Structure

In this fully mapped scheme, each directory entry contains  $N_{Caches}$  bits for a total storage requirement of

$$Bits = N_{Caches} * N_{MemoryLines}$$

$$= O(N_{Caches} N_{MemoryLines})$$

where  $N_{Caches}$  is the number of caches and  $N_{MemoryLines}$  is the number of memory lines in the system.

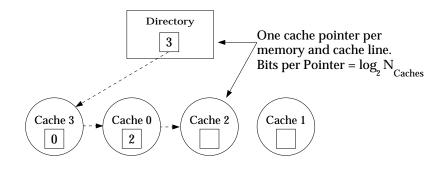

## 3.1.2 Distributed Directory

In a distributed directory (DD) protocol, a linked list structure is used to maintain the list of caches that have a copy of a given memory line. The directory entry contains a pointer to the head of this list, and each cache line contains the necessary pointers to construct the list. The list may be singly-linked or doubly-linked. It is important to note that the order of the list is not optimized in any way. The order is determined by the order that the requests for the memory line reach the directory.

## Singly-Linked Directory Structures

In a singly-linked distributed directory protocol [70], a singly-linked list is used to maintain the list as shown in figure 3.2. In this example, caches 0, 2 and 3 have a copy of the line.

Figure 3.2: Singly-Linked Distributed Directory Structure

In this case, each directory entry contains  $log_2(N_{Caches})$  bits, and each cache line must also include a single pointer. The directory now requires a total of

$$Bits = N_{MemoryLines}log_2(N_{Caches}) + N_{CacheLines}log_2(N_{Caches})$$

$$= log_2(N_{Caches})(N_{MemoryLines} + N_{CacheLines})$$

$$= O(log_2(N_{Caches})N_{MemoryLines})$$

which scales better than the fully-mapped CD directory structure as the size of the system ( $N_{Caches}$  and  $N_{MemoryLines}$ ) increases.

#### **Doubly-Linked Directory Structures**

Alternatively, a doubly-linked directory structure may be used [42], as shown in figure 3.3. In this example, caches 0, 2 and 3 have a copy of the line.

Figure 3.3: Doubly-Linked Distributed Directory Structure

The amount of storage required is slightly more than that of the singly-linked distributed directory structure since each cache line must now maintain two pointers. The directory now requires

$$Bits = N_{MemoryLines} log_2(N_{Caches}) + 2N_{CacheLines} log_2(N_{Caches})$$

$$= log_2(N_{Caches})(N_{MemoryLines} + 2N_{CacheLines})$$

$$= O(Log_2(N_{Caches})N_{MemoryLines})$$

of total storage.

## 3.1.3 Scalability of Directory Structures

As shown above, the centralized directory structure scales as  $O(N_{Caches}N_{MemoryLines})$ , while the distributed directories scale better as  $O(log_2(N_{Caches})N_{MemoryLines})$ . However, several different approaches have been suggested to improve the scalability of the centralized directory schemes. These include limited pointer schemes and cached directories.

The limited pointer schemes limit the number of cached copies of each memory line. When this limit is exceeded, the limited pointer schemes either invalidates one of the copies to make room for the new request [4], assumes all caches now have a copy of the line [4], switches to a coarse grain mode where each bit represents several caches [39] or traps to software to extend the directory list [14]. With a limited pointer scheme, the centralized directory scales as  $O(N_{Limited} N_{MemoryLines})$  where  $N_{Limited}$  is the number of bits in the limited directory entry.

The other approach notes that the maximum number of cached copies of a memory line is limited by the total size of all caches and not by the size of memory. In this case, a directory cache could be used to cache this smaller set of directory entries [39]. Also, the bits for each directory entry can be dynamically allocated out of a pool of directory bits [62].

Several studies have suggested that the average number of shared copies of a memory line is small [13, 57, 71, 4, 26]. The results presented by the researchers demonstrate that the limited directory schemes result in a minimal performance loss [4, 14, 39], and similarly, the cached directory has also been shown to have a minimal affect on performance [39]. These results are *very* dependent on the number of shared copies of a line in a given application.

Some of the limited pointer schemes require that the directory be able to invalidate cached copies of a line. The centralized directory update-based protocol presented in this work currently does not support invalidations, but the protocol could be extended to support such directory initiated invalidations.

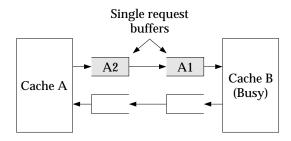

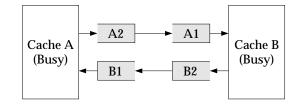

# 3.2 Protocol Deadlock

If the system has finite buffering, then protocol level deadlock is possible [69, 53, 35]<sup>1</sup>. For example, figure 3.4 shows two caches that are sending requests to each other through a set of finite buffers. Each buffer can hold a single request. First, cache A sends two requests to cache B, and it begins processing a request that will generate another request to cache B. But because the buffers are already full, cache A must wait until a buffer becomes available before it is able to complete the processing of the new request. Meanwhile, cache B generates two requests to cache A, and it attempts to generate a third request. The system is now deadlocked. Neither cache A nor B can complete the processing of their current request because their output buffers are full, and they will never empty. A timeout must be used to detect such deadlocked

<sup>&</sup>lt;sup>1</sup>The actual network is assumed to be deadlock free.

(a) Cache A sends two requests to Cache B which is currently busy. Cache A begins processing a request that will generate another request for Cache B.

(a) Cache A cannot complete current request since the buffer is full. Meanwhile, Cache B generates two requests to Cache A and attempts to generate a third request. Neither cache can proceed since their output buffers are full. The system is deadlocked.

Figure 3.4: Protocol Level Deadlock

situations. Once detected, there are two basic techniques to handle deadlock.